# Monolithically integrated 112 Gbps PAM4 optical transmitter and receiver in a 45nm CMOS-silicon photonics process

THOMAS BAEHR-JONES, SHAHAB ARDALAN, MATTHEW CHANG, SAMAN JAFARLOU, XAVIER SEREY, GEORGE ZARRIS, GABRIEL THOMPSON, ARTSROUN DARBINIAN, BRIAN WEST, BABAK BEHNIA, VESSELIN VELEV, YUN ZHE LI, KATHERINE ROELOFS, WUCHUN WU, JIM MALI, JIAHAO ZHAN, NOAM OPHIR, CHRIS HORNG, ROMANAS NAREVICH, FEN GUAN, JINGHUI YANG, HAO WU, PATRICK MAUPIN, RHYS MANLEY, YOGI AHUJA, ARI NOVACK, LEI WANG, AND MATTHEW STRESHINSKY\*

Luminous Computing, 4750 Patrick Henry Dr, Santa Clara, CA 95054 \*matthew.streshinsky@lmns.com

Abstract: We demonstrate a transmitter and receiver in a silicon photonics platform for Oband optical communication that monolithically incorporates a modulator driver, travelingwave Mach-Zehnder modulator, control circuitry, photodetector, and TIA in the GlobalFoundries Fotonix<sup>™</sup> (45SPCLO) platform. The transmitter and receiver show an open 112 Gbps PAM4 eye at a 4.3 pJ/bit energy efficiency, not including the laser. Extensive use of gain-peaking enables our modulator driver and TIA to achieve the high bandwidths needed in the 45 nm CMOS-silicon photonics process. Our results suggest an alternative to the frequent approach of bump-bonding BiCMOS drivers and TIAs to silicon photonics.

### 1. Introduction

Performance per Watt is one of the critical metrics by which a computer system is judged. The numerator, performance, is typically expressed as the number of operations per second performed when the computer system is operating at peak throughput. The denominator, Watts, is the overall power consumption of the system during this period. Power dissipated in the processors, switches, communication links, power supplies, memory, cooling systems, and associated supporting infrastructure all contribute to the denominator. As overall bandwidths increase, the power required for data movement in an exascale computing system becomes a significant contributor to the power consumption of a system. Existing systems implement more than 1000 Pbps of total memory bandwidth [1]. A future disaggregated memory system could see further scaling with a significant fraction of the bandwidth transmitted in the optical domain [2]. In terms of energy efficiency of such links, an end-to-end optical link using pluggable optics may consume on the order of 25 pJ/bit, including the SERDES in the host ASIC [3]. At 2000 Pbps of bidirectional traffic and 25 pJ/bit, the power dissipated in optical links would multiply to 50 MW for such an optically-connected memory system, significantly more than the entire system power of existing Top500 HPC systems [4]. Here, we have ignored the power from optical links to support switching and other functionality to express orders-of-magnitude. It follows that continued bandwidth scaling for new computer architectures will require further improvements in the energy efficiency of optical links in order to preserve or improve performance per Watt.

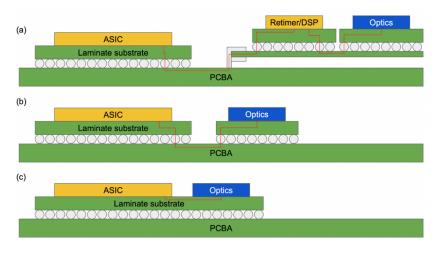

Fig. 1. (a) A conventional optical link from an ASIC on a host PCB to a pluggable optical module with a retimer or DSP chip. (b) An alternative link in which the optical engine is placed in a package near the ASIC, (c) Co-packaged optics in which the optical engine is on the same substrate as the ASIC. The arrangements shown in (b) and (c) provide net power consumption savings over (a) by eliminating the retimer/DSP chip.

Co-packaged optics improves the performance per Watt of computer systems by eliminating the need for additional electrical retimer chips, such as those used in conventional pluggable optics. Fig. 1(a) shows an illustration of the electrical connectivity from a host ASIC (a switch or processor, for example) to a pluggable optical module that provides the interface to optical fibers. Inside of the pluggable module, it is common to include a DSP chip, which converts the host-side interface, such as 8x50 Gbps signaling, into an optical interface, such as 4x100 Gbps signaling [5]. Crucially, the DSP chip also provides retiming and equalization functionality, as closing the full link from the ASIC through the pluggable connector to the optics directly would be too challenging. Fig. 1(b,c) shows example links in which the DSP chip is not required. In (b), the separately-packaged optical engine is located near the ASIC, similar to the orientation inside of the pluggable, while in (c), the optical engine and the ASIC are co-packaged together. While both (b) and (c) eliminate the DSP chip, the co-packaged solution requires less signal equalization, which in turn can lead to improved optical sensitivity and/or lower electrical power consumption within the SERDES.

The requirements of a co-packaged optical link motivate a technology that can support high-density I/O and excellent energy efficiency [6,7]. To meet these needs, silicon photonics (SiPh) emerges as a promising platform for next-generation interconnects because of the ease with which it is possible to take advantage of existing multi-chip module assembly infrastructure [8,9]. In particular, a monolithic CMOS+SiPh process is ideal for CPO because it enables: (1) Device density that exceeds conventional pad-pitch limitations of wirebond, flip-chip, or advanced packaging techniques, (2) simplified electrical assembly compared to heterogeneous electrical amplifier and photonics chipsets, and (3) close integration between ASICs and optical I/O [10-12].

However, one large disadvantage of a monolithic CMOS-SiPh process is that, typically, the performance of the CMOS is not state-of-the-art [13]. Thus, an open question exists whether such monolithic CMOS-SiPh processes can enable optical links at the latest-generation of bit rates, modulation formats, and SERDES capabilities. Importantly, for most chip-to-chip communications inside of exascale compute systems, this typically requires interoperability with the interfaces that support PCB or backplane communications. If a link can be connected electrically rather than optically, it typically should from an energy & cost perspective. It is also desirable to be able to use a single ASIC design for both electrical

connectivity and optical connectivity. Thus, interfacing optics to ASICs at the latest generation of standard 112 Gbps, or similar, rates enables a flexible I/O architecture.

Designing both a transmitter and a receiver in a monolithic CMOS-SiPh process at these data rates is as of yet undemonstrated in literature. Many results have demonstrated heterogeneous chipsets integrated in a 2D, 2.5D, or 3D assembly with separate electrical ICs and photonic ICs [3, 5, 14-21]. Prior monolithic literature with both a transmitter and receiver on-wafer demonstrated links at up to 25 Gbps [22-24] with published simulation models for a monolithic die at 106 Gbps [25]. Prior individual monolithic results (i.e., only a transmitter or only a receiver) demonstrate a transmitter at 44 Gbps NRZ [26], a receiver at 56Gbps NRZ [27], and a coherent receiver at up to 66 Gbaud QPSK [28], all in a SiGe BiCMOS-SiPh monolithic process; as well as a 100 Gbps PAM4 transmitter [29], a 56 Gbps PAM4 transmitter [30], and separately a 28 Gbps NRZ receiver [31] in a CMOS-SiPh process.

In this manuscript, we describe in detail the first CMOS-SiPh monolithic transmitter and receiver for 112 Gbps optical communication designed and fabricated in the GlobalFoundries Fotonix<sup>TM</sup> (45SPCLO) platform. The chips operate near 1310 nm and monolithically incorporate all the electrical and optical functionality for an optical transmitter and receiver, except for the laser which is packaged separately and fiber-coupled. The transmitter (TX) and receiver (RX) photonic-analog chips (PAC) are fabricated on the same wafer without any process modifications between the two designs. The TX PAC comprises a linear modulator driver, traveling-wave Mach-Zehnder (TWMZ) modulator, an integrated feedback control system, and digital serial peripheral interface (SPI). The RX PAC comprises an integrated photodetector, linear transimpedance amplifier (TIA), and a separate SPI bus. Both the TX PAC and RX PAC are shown to operate with open eyes at 112 Gbps PAM4.

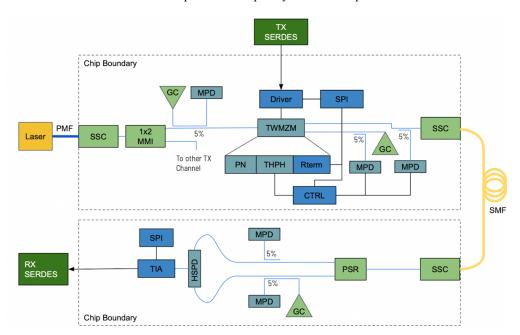

Fig. 2. Schematic representation of the on-chip signal path, including spot-size converter (SSC), 1x2 laser splitter, monitor photodiodes (MPD), serial peripheral interface (SPI) for control, traveling wave Mach-Zehnder modulator (TWMZM), high-speed pn-junction phase shifter (PN), thermal phase shifter (THPH), adjustable termination resistor (Rterm), high-speed photodetectors (HSPD), polarization splitter & rotators (PSR), grating couplers for testing (GC), and integrated control system (CTRL).

# 2. Design and Fabrication

The transmitter and receiver are designed as separate chips on the same reticle and wafer. No process splits are utilized between the two chips. Each TX PAC contains 16 channels with 8 total laser inputs where each laser is split two ways. Each RX PAC also contains 16 channels with on-chip polarization diversity. V-groove edge couplers are used as spot-size converters between optical fibers and on-chip waveguides [12]. Grating-couplers are used throughout both chips for wafer-level and some chip-level testing. Refer to Fig. 2 for a schematic representation of the on-chip signal paths.

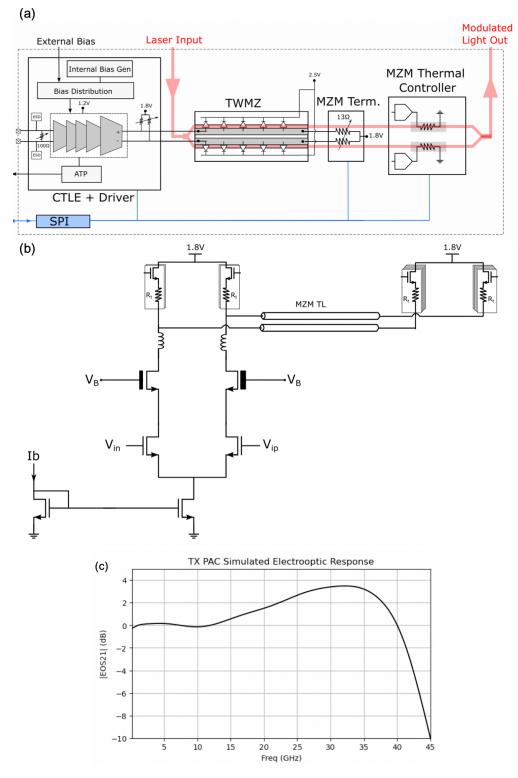

A current mode driver chain is used to drive a differential TWMZ that is terminated by an adjustable termination resistor [32]. The pn junctions in each arm are each driven in push-pull configuration and see the full drive voltage, with an overall differential transmission line [33,34]. Therefore, the driver is designed to be loaded by a 24  $\Omega$  differential impedance transmission line and provide 1.6 V peak-to-peak differential voltage. In combination with the modulator, the TX PAC is calculated to achieve a low-frequency phase shift of 1.1 radians. During operation, applied equalization will lower the total modulation depth. The driver chain consists of an input termination followed by 5 CML stages. The input of the driver chain is matched to a 100  $\Omega$  differential resistor and DC coupled with a common mode voltage of 650 mV.

All driver stages are CML-based amplifiers with different functionalities, as shown in Fig. 3(a). The input stage is sized to provide minimum capacitive loading at the input to achieve low input return loss. The second stage is a CTLE with switchable RC source degeneration to provide high frequency peaking for bandwidth improvement. The third stage is a variable gain amplifier (VGA) to adjust the driver gain. The input termination and CML stages benefit from T-coils at their output to improve the bandwidth. The last stage of the driver, shown in Fig. 3(b), is a cascode CML stage with thick oxide FETs as output devices to tolerate high output swing. In order to achieve the optimal linear swing, the output stage is powered using a 1.8 V supply. The driver is double-terminated with adjustable resistors to reduce the reflections at both ends. However, the termination on the driver side must be kept higher to preserve the voltage swing amplitude. Fig. 3(c) plots the simulated |EOS21| response of the PAC-TX from driver input to fiber output at nominal process and temperature corners.

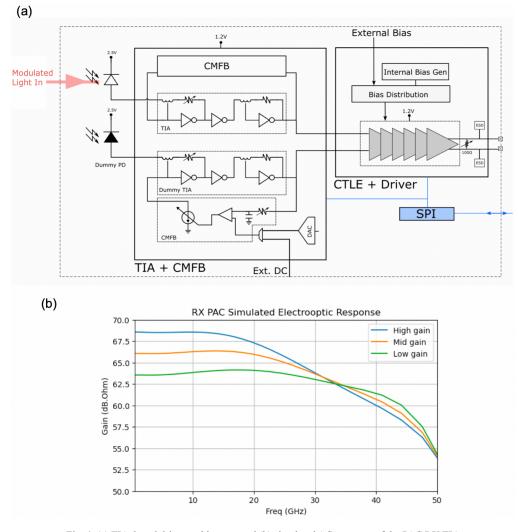

The RX lane architecture is shown in Fig. 4(a). An illuminated single-ended photodiode drives a balanced RX implementation. A dark photodiode is connected to the complementary RX input. The first stage is a pseudo-differential inverter-based shunt-feedback TIA, followed by an inverter-based Cherry-Hooper amplifier. Both inverter-based stages have symmetric T-coil inductive peaking [35] and are powered by an externally regulated low-noise power supply. The subsequent stages are implemented as fully differential CML-based amplifiers with no supply regulation. The first CML stage performs single-ended to differential (S2D) conversion, followed by a programmable continuous-time linear equalization (CTLE), a programmable gain amplifier (PGA), a pre-driver, and an output pad driver. Most CML stages use bridged-shunt inductive peaking networks, chosen for robustness, while the pad driver has a symmetric T-coil network for broadband output matching [36].

Fig. 3. (a) Modulator driver architecture, (b) output driver stage schematic diagram, and (c) simulated |EOS21| response of the TX PAC.

Independent common-mode feedback circuits sense the output of each Cherry-Hooper amplifier and feed back a DC current into the respective photo-detector anode. This scheme allows for optimal S2D input common-mode biasing, and the use of independent voltage references allow for foreground offset calibration. The low-pass filter cut-off is lower than 50 kHz, resulting in negligible baseline wander at 112 Gbps. On-chip current and voltage generators bias the RX, and an SPI interface allows for digital programming of internal registers. At high gain, simulated noise at 30 GHz is 17.7 pA/Hz<sup>1/2</sup>. Fig 4(b) plots the simulated AC response at three different gain settings.

Fig. 4. (a) TIA & pad driver architecture and (b) simulated AC response of the PAC RX TIA loaded with the photodetector at three different gain settings.

The wafers are fabricated in GlobalFoundries' 300 mm 45 nm SOI process (GF Fotonix<sup>TM</sup>). The wafers monolithically integrate high-speed transistors, modulators, photodetectors, ridge waveguides, rib waveguides, silicon nitride waveguides, V-groove edge couplers, and a full metal stack.

## 3. Experimental Results

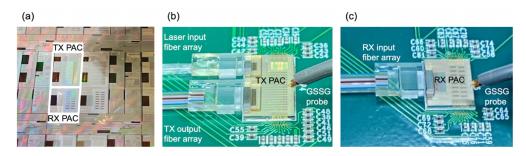

The transmitter and receiver chips are designed for co-packaged applications wherein the fullflow wafers are bumped with V-groove edge couplers and the high-speed I/O are directly connected to the host ASIC SERDES. High-speed probes are used for testing the individual performance of the transmitter and receiver since the flip-chip substrate application circuit limits access to the high-speed inputs and outputs of the chip. Fig. 5. shows photographs of the full transmitter and receiver chips, as well as the devices under test. The TX PAC uses a separate glass array of polarization-maintaining fibers for laser inputs and standard singlemode fibers for modulator outputs. The RX PAC uses a single array of standard single-mode fiber. The low-speed I/O and power supplies are connected via wirebonds to a printed circuit board while the high-speed I/O is probed in a ground-signal-signal-ground configuration for both TX and RX PACs.

Fig. 5. Photographs of (a) the TX and RX chips on-wafer, (b) the TX PAC under test, and (c) the RX PAC under test.

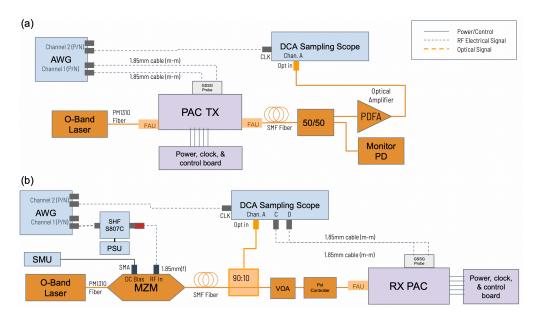

Fig. 6 shows a block diagram of the transmitter and receiver test setups. A Keysight M8194A arbitrary waveform generator (AWG) generates the high-speed PAM4 signal, while a Keysight DCA-N1092C oscilloscope (DCA) captures the signal. An FPGA and microcontroller are used to communicate to the on-chip SPI and external DC power supplies provide power and biasing. For receiver characterization, an external EOSpace 40 GHz lithium niobate modulator is used to generate the input optical waveform. For all testing, the laser outputs near 1310nm.

The TX PAC is tested with a 50mW input in the PM fiber. On-chip, each laser input is split once so that each channel requires approximately 25mW of laser power. The PDFA optical amplifier is used to amplify the Tx output to approximately 0 dBm before entering the DCA. During operation, the on-chip control loops bias and stabilize the thermal tuner inside the TWMZ. A SPI command is used to flip a single polarity bit that determines whether the control loop stabilizes on a rising edge or falling edge of the Mach-Zehnder transfer function. On-chip ADCs, DACs, low-speed TIAs, and low dropout voltage regulators sample the MPD photocurrent and drive the thermal tuners. During transmitter output eye diagram characterization, the s-parameter response for the 1.85 mm cabling up to the probe input (but not including the probe or TX PAC) is equalized from the AWG output. A 5-tap T-spaced feed forward equalizer is then optimized & applied at the AWG to compensate for the probe and TX PAC electro-optic response. The measured fiber-to-fiber insertion loss of the transmitter when biased at the maximum TWMZ transmission point is 15.3 dB; we note this includes an intrinsic 3 dB loss for splitting each laser into two channels.

Fig. 6. Block diagram of the (a) transmitter and (b) receiver experimental test setup.

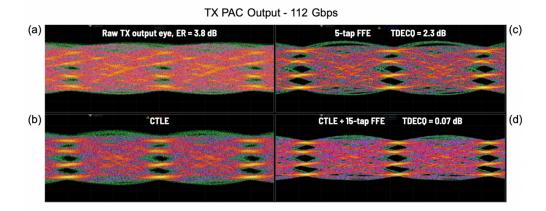

At 112 Gbps we measure clean open eyes from the TX PAC, as shown in Fig. 7. We characterize TDECQ out of the transmitter under a variety of scenarios. TDECQ (transmitter and dispersion eye closure quaternary) is a figure of merit for the eye quality of PAM4 optical transmitters [37]. The TX PAC measures an extinction ratio of 3.8 dB and a TDECQ of 2.3 dB with a standard 5-tap feed forward equalizer (FFE) which meets the IEEE 802.3 requirement for a 400GBASE-DR4 transmitter. With the aid of a continuous time linear equalizer (CTLE) analog filter and additional FFE taps, the TX eye opens up further, indicating that an improved |S21| response in a redesigned device would further improve our measured TDECQ. The CTLE filter implemented on the DCA has a 21 GHz zero, 27 GHz first pole, and 32 GHz second pole.

Fig 7. Measured eye diagrams from TX PAC testing at 112 Gbps with various filters implemented on the DCA, sampled with a baud/2 bandwidth receiver: (a) A "raw" TX without further signal processing; (b) processed with an analog CTLE where the CTLE has a 21 GHz zero, 27 GHz first pole, and 32 GHz second pole; (c) with a 5-tap FFE; and (d) with the CTLE and a 15-tap FFE.

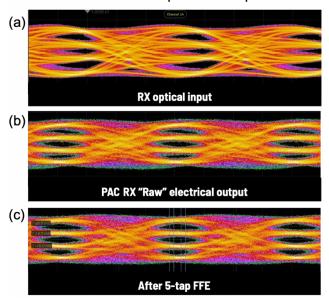

Similar to the TX PAC performance, the PAC RX also shows open eyes when tested at 112 Gbps. A modulated signal from the reference modulator with mean power of 1.0 mW is input at the SM fiber. Measured fiber-referred high-speed photodiode responsivity for the assembly under test is 245 mA/W for TE-polarized and 210 mA/W for TM-polarized input light, corresponding to 0.7 dB polarization-dependent loss. Fig. 8 shows the optical input to the PAC RX from the reference modulator in (a), the sampled eye after a baud/2 receiver in (b), and the filtered eye after a feed forward equalizer in (c). At 112 Gbps, only a 5-tap FFE is required to open the eye, well within the capabilities of an LR SERDES. Many long reach SERDES also implement CTLE and/or a decision feedback equalizer, which could further improve performance [38-40].

In operation our modulator driver, TIA, biasing, and active control require 483 mW. At 112 Gbps, this corresponds to 4.3 pJ/bit, not including the laser or SERDES. Future TX PAC devices may incorporate a local undercut, which would reduce the required thermal tuning power. A breakdown of the power consumption is shown in Table 1. All values are measurements except for the heater and associated drive circuitry overhead, which is projected at a required optical phase shift of  $\pi/2$  radians.

RX PAC Output - 112 Gbps

Fig. 8. Measured eye diagrams from RX PAC testing at 112 Gbps. Shown in (a) is the optical input from the reference modulator used as stimulus. (b) Shows the "raw" eye after a baud/2 bandwidth sampler in the DCA and (c) shows the eye after a 5-tap FFE.

| Component                                     | Measured Power<br>Consumption (mW) | Energy Efficiency at 112<br>Gbps (pJ/bit) |

|-----------------------------------------------|------------------------------------|-------------------------------------------|

| Modulator & driver                            | 312                                | 2.8                                       |

| TIA                                           | 114                                | 1.0                                       |

| Mixed signal TWMZ control                     | 7.6                                | 0.1                                       |

| Heater and drive circuitry overhead (Typical) | 49 <i>a</i>                        | 0.4                                       |

| Total (Typical)                               | 483                                | 4.3                                       |

Table 1. Breakdown of power consumption for the TX PAC and RX PAC and extrapolation to typical total power consumption for transmitter and receiver

<sup>*a*</sup> Projected average value for the expected intrinsic phase error to be corrected of  $\pi/2$ .

# 4. Conclusion

Monolithic CMOS-silicon photonics processes are attractive platforms for next-generation co-packaged optics applications. A critical unanswered question up to now is whether such platforms are capable of operating at high-speed, particularly in 45 nm CMOS. We demonstrate that such a monolithic platform is suitable for 112 Gbps optical communications. Co-packaging these transmitter and receiver chips with a processor, switch, or other ASIC will ultimately result in improvements in computer system performance per Watt compared to what would be achieved by utilizing conventional pluggable optics.

Acknowledgments. The authors would like to thank Anthony Yu and the GlobalFoundries team for their support during the development and fabrication of these chips. Special thanks go to Jenny Huang and Adrian Chang for the assembly of the tested modules. The authors would also like to thank our CEO, Marcus Gomez; CTO, Mitchell Nahmias; president, Michael Hochberg; SVP of engineering, Dominick Scordo; chief architect, David Baker; program manager, Jonathan Centofanti; and entire Luminous Computing team for their invaluable support, guidance, and discussions.

Disclosures. The authors declare no conflicts of interest.

#### References

- 1. "Specifications Supercomputer Fugaku : Fujitsu Global" https://www.fujitsu.com/global/about/innovation/ fugaku/specifications/.

- Jorge Gonzalez, Alexander Gazman, Maarten Hattink, Mauricio G. Palma, Meisam Bahadori, Ruth Rubio-Noriega, Lois Orosa, Madeleine Glick, Onur Mutlu, Keren Bergman, and Rodolfo Azevedo, "Optically connected memory for disaggregated data centers." Journal of Parallel and Distributed Computing 163, 300-312 (2022).

- Radhakrishnan Nagarajan, Liang Ding, Roberto Coccioli, Masaki Kato, Ronson Tan, Pushkraj Tumne, Mark Patterson, and Linda Liu, "2.5D Heterogeneous Integration for Silicon Photonics Engines in Optical Transceivers," IEEE Journal of Selected Topics in Quantum Electronics 29(3), 1-10 (2022).

- 4. https://www.top500.org/.

- Chongjin Xie, Peter Magill, David Li, Yinxing Zhang, Long Zheng, Anbin Wang, Yun Bao, Chunchun Sui, Matthew Streshinsky, Jianwei Mu, Sigeng Yang, and Wanju Sun, "Real-Time Demonstration of Silicon-Photonics-Based QSFP-DD 400GBASE-DR4 Transceivers for Datacenter Applications," *Optical Fiber Communication Conference, OSA Technical Digest* (OFC 2020), paper T3H.5 (2020).

- Cyriel Minkenberg, Rajagopal Krishnaswamy, Aaron Zilkie, and David Nelson, "Co-packaged datacenter optics: Opportunities and challenges," IET Optoelectronics 15, 77-91 (2021).

- Benjamin G. Lee, Nikola Nedovic, Thomas H. Greer III, and C. Thomas Gray, "Beyond CPO: A Motivation and Approach for Bringing Optics Onto the Silicon Interposer," IEEE Journal of Lightwave Technology 41(4), 1152-1162 (2023).

- Marc Bohn, Peter Magill, Michael Hochberg, Dominick Scordo, Ari Novack, and Matthew Streshinsky, "Next-Generation Silicon Photonic Interconnect Solutions," *Optical Fiber Communication Conference, OSA Technical Digest* (OFC 2019), paper M3J.3 (2019).

- 9. Michal Lipson, "The revolution of silicon photonics," Nature Materials 21, 974–975 (2022).

- Vladimir Stojanovic, Rajeev J. Ram, Milos Popovic, Sen Lin, Sajjad Moazeni, Mark Wade, Chen Sun, Luca Alloatti, Amir Atabaki, Fabio Pavanello, Nandish Mehta, and Pavan Bhargava, "Monolithic silicon-photonic platforms in state-of-the-art CMOS SOI processes," Optics Express 26(10), 13106-13121 (2018).

- Ken Giewont, Karen Nummy, Frederick A. Anderson, Javier Ayala, Tymon Barwicz, Yusheng Bian, Kevin K. Dezfulian, Douglas M. Gill, Thomas Houghton, Shuren Hu, Bo Peng, Michal Rakowski, Stewart Rauch III, Jessie C. Rosenberg, Asli Sahin, Ian Stobert, and Andy Stricker, "300-mm Monolithic Silicon Photonics Foundry Technology," IEEE Journal of Selected Topics in Quantum Electronics 25(5), 1-11 (2019).

- 12. Michal Rakowski, Colleen Meagher, Karen Nummy, Abdelsalam Aboketaf, Javier Ayala, Yusheng Bian, Brendan Harris, Kate Mclean, Kevin McStay2, Asli Sahin, Louis Medina, Bo Peng, Zoey Sowinski, Andy Stricker, Thomas Houghton, Crystal Hedges, Ken Giewont, Ajey Jacob, Ted Letavic, Dave Riggs, Anthony Yu, and John Pellerin, "45nm CMOS - Silicon Photonics Monolithic Technology (45CLO) for next-generation, low power and high speed optical interconnects," *Optical Fiber Communication Conference, OSA Technical Digest* (OFC 2020), paper T3H.3 (2020).

- Matthew Streshinsky, Ran Ding, Yang Liu, Ari Novack, Christophe Galland, Andy E.-J. Lim, P. Guo-Qiang Lo, Thomas Baehr-Jones, and Michael Hochberg, "The road to affordable, large-scale silicon photonics." Optics and Photonics News 24(9): 32-39 (2013).

- 14. Jacob S. Levy, Erman Timurdogan, Yu-Sheng Kuo, Gap Youl Lyu, Charles Tsai, Xuejin Yan, Harqkyun Kim, Cristian Stagarescu, Kevin Meneou, Abu Thomas, Ioannis Fragkos, Geoffrey Sitwell, Andrea Trita, Yangyang Liu, Melissa Ziebel, Jerry Byrd, Sven Steinbach, Bruce Chou, William Vis, Arin Abed, Young Kwon, Henri Nykäne, Shih-Han Lo, Janne Ikonen, Juha Larismaa, John Drake, Albert Benzoni, Cyriel Minkenberg, Thomas Schrans, and Andrew Rickman, "4x100Gb/s PAM4 Multi-Channel Silicon Photonic Chipset with Hybrid Integration of III-V DFB Lasers and Electro-Absorption Modulators," IEEE Journal of Lightwave Technology Early Access, 1-10 (2023).

- Ying Zhao, Li Chen, Ricardo Aroca, Ninghui Zhu, Dinh Ton, David Inglis and Christopher Doerr, "Silicon Photonic Based Stacked Die Assembly for 4×200-Gbit/s Short-Reach Transmission," *Optical Fiber Communication Conference, OSA Technical Digest* (OFC 2021), paper F2F.2 (2021).

- Erman Timurdogan, Zhan Su, Ren-Jye Shiue, Matthew J. Byrd, Christopher V. Poulton, Kenneth Jabon, Christopher DeRose, Benjamin R. Moss, Ehsan S. Hosseini, Ivan Duzevik, Michael Whitson, Ronald P. Millman, Jr., Dogan A. Atlas and Michael R. Watts, "400G Silicon Photonics Integrated Circuit Transceiver Chipsets for CPO, OBO, and Pluggable Modules," *Optical Fiber Communication Conference, OSA Technical Digest* (OFC 2020), paper T3H.2 (2020).

- Matt Traverso, Marco Mazzini, Kumar Lakshmikumar, Sanjay Sunder, Alex Kurylak, Craig Appel, Cristiana Muzio, Ravi Tummidi, Alberto Cervasio, Mary Nadeau, Weizhuo Li, Jarrett Neiman, and Mark Webster, "Integrated Silicon Photonics Transceiver Module for 100Gbit/s 20km Transmission," *Optical Fiber Communication Conference, OSA Technical Digest* (OFC 2021), paper M3A.3 (2021).

- Radhakrishnan Nagarajan, Mark Filer, Yang Fu, Masaki Kato, Todd Rope, and James Stewart, "Silicon Photonics-Based 100 Gbit/s, PAM4, DWDM Data Center Interconnects," Journal of Optical Communications and Networking 10(7), B25-B36 (2018).

- Saeed Fathololoumi, Christian Malouin, David Hui, Kadhair Al-hemyari, Kimchau Nguyen, Pegah Seddighian, Yen-Jung Chen, Ye Wang, Aidong Yan, Reece Defrees, Thomas Liljeberg, and Ling Liao, "Highly Integrated 4 Tbps Silicon Photonic IC for Compute Fabric Connectivity," 2022 IEEE Symposium on High-Performance Interconnects (HOTI), 1-4 (2022).

- Vivek Raghunathan, Karl Muth, Bapiraju Vinnakota, Prasad Venugopal, Rebecca Schaevitz, and Manish Mehta, "SCIP to the Next Generation of Computing: Extending More than Moore with Silicon Photonics Chiplets in Package (SCIP)," 2022 23rd International Symposium on Quality Electronic Design (ISQED), 1-6 (2022).

- Rang-Chen Yu and Dong Pan, "Silicon Photonics Applications for 5G and Data Centers," Optical Fiber Communication Conference, OSA Technical Digest (OFC 2021), paper M3A.5 (2021).

- 22. Thierry Pinguet, Peter M. De Dobbelaere, Dennis Foltz, Steffen Gloeckner, Steven Hovey, Yi Liang, Michael Mack, Gianlorenzo Masini, Attila Mekis, Mark Peterson, Thierry Pinguet, Subal Sahni, Jeff Schramm, Michael Sharp, Lieven Verslegers, Brian P. Welch, Kosei Yokoyama, Shuhuan Yu, "25 Gb/s Silicon Photonic Transceivers," *The 9th International Conference on Group IV Photonics (GFP 2012)*, paper ThC1 (2012).

- Francesco Testa, Mark T. Wade, Mikael Lostedt, Fabio Cavaliere, Marco Romagnoli, and Vladimir Stojanovic, "Optical Interconnects for Future Advanced Antenna Systems: Architectures, Requirements and Technologies," IEEE Journal of Lightwave Technology 40(2), 393–403 (2022).

- James F. Buckwalter, Xuezhe Zheng, Guoliang Li, Kannan Raj, Fellow, IEEE, and Ashok V. Krishnamoorthy, "A Monolithic 25-Gb/s Transceiver With Photonic Ring Modulators and Ge Detectors in a 130-nm CMOS SOI Process," IEEE Journal of Solid-State Circuits 47(6), 1309–1322 (2012).

- Christoph Schulien, "Enabling Scalable Application-Specific Optical Engines (ASOE) by Monolithic Integration of Photonics and Electronics," 2022 IEEE Hot Chips 34 Symposium (HCS), 1-32 (2022).

- Festim Iseini, Mesut Inac, Andrea Malignaggi, Anna Peczek, and Gerhard Kahmen, "Monolithically Integrated Optoelectronic Transmitter based on Segmented Mach-Zehnder Modulator in EPIC 250 nm BiCMOS Technology," in 2023 IEEE 23rd Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, 51-54 (2023).

- Giannino Dziallas, Adel Fatemi, Anna Peczek, Lars Zimmermann, Andrea Malignaggi, and Gerhard Kahmen, "A 56-Gb/s Optical Receiver With 2.08-μA Noise Monolithically Integrated into a 250-nm SiGe BiCMOS Technology, IEEE Transactions on Microwave Theory and Techniques **70**(1), 392–401 (2022).

- Pascal M. Seiler, Karsten Voigt, Anna Peczek, Galina Georgieva, Stefan Lischke, Andrea Malignaggi, and Lars Zimmerman, "Multiband Silicon Photonic ePIC Coherent Receiver for 64 GBd QPSK," IEEE Journal of Lightwave Technology 40(10), 3331–3337 (2022).

- 29. Mark Wade, Erik Anderson, Shahab Ardalan, Pavan Bhargava, Sidney Buchbinder, Michael L. Davenport, John Fini, Haiwei Lu, Chen Li, Roy Meade, Chandru Ramamurthy, Michael Rust, Forrest Sedgwick, Vladimir Stojanovic, Derek Van Orden, Chong Zhang, and Chen Sun, "TeraPHY: A Chiplet Technology for Low-Power, High-Bandwidth In-Package Optical I/O," IEEE Micro 40(2), 63-71 (2020).

- Chi Xiong, Douglas M. Gill, Jonathan E. Proesel, Jason S. Orcutt, Wilfried Haensch, and William M. J. Green, "Monolithic 56 Gb/s silicon photonic pulse-amplitude modulation transmitter," Optica 3(10), 1060–1065 (2016).

- Solomon Assefa, Huapu Pan, Steven Shank, William M. J. Green, Alexander Rylyakov, Clint Schow, Marwan Khater, Swetha Kamlapurkar, Edward Kiewra, Carol Reinholm, Teya Topuria, Philip Rice, Christian Baks, and Yurii Vlasov, "Monolithically Integrated Silicon Nanophotonics Receiver in 90nm CMOS Technology Node," in *Optical Fiber Communication Conference, OSA Technical Digest* (Optical Society of America, 2013), paper OM2H.4.

- 32. Mayank Raj, Yohan Frans, Ping-Chuan Chiang, Sai Lalith Chaitanya Ambatipudi, David Mahashin, Peter De Heyn, Sadhishkumar Balakrishnan, Joris Van Campenhout, Jimmy Grayson, Marc Epitaux, and Ken Chang, "Design of a 50-Gb/s Hybrid Integrated Si-Photonic Optical Link in 16-nm FinFET," IEEE Journal of Solid-State Circuits 55(4), 1086-1095 (2020).

- Jeremy Witzens, Thomas Baehr-Jones, and Michael Hochberg, "Design of transmission line driven slot waveguide Mach-Zehnder interferometers and application to analog optical links," Optics Express 18(16), 16902-16928 (2010)

- 34. Jeremy Witzens, "High-Speed Silicon Photonics Modulators," in *Proceedings of the IEEE* **106**(12), 2158-2182 (2018)

- Sudip Shekhar, Jeffrey S. Walling, and David J. Allstot, "Bandwidth Extension Techniques for CMOS Amplifiers," IEEE Journal of Solid-State Circuits 41(11), 2434-2439 (2006).

- Behnam Analui, Drew Guckenberger, Daniel Kucharski, and Adithyaram Narasimha, "A Fully Integrated 20-Gb/s Optoelectronic Transceiver Implemented in a Standard 0.13-μm CMOS SOI Technology," IEEE Journal of Solid-State Circuits 41(12), 2945-2955 (2006).

- 37. "IEEE Standard for Ethernet," in *IEEE Std 802.3-2022* (Revision of *IEEE Std 802.3-2018*) (2022).

- J. W. Kim, Stanley Chen, Y. Wang, H.-W. Hung, K. Tan, W. Lin, Arianne Bantug Roldan, D. Carey, Ilias Chlis, Ronan Casey, A. Bekele, Y. Cao, D. Mahashin, H. Ahn, H. Zhang, Y. Frans, and K. Chang, "A 112-Gb/s PAM-4 Long-Reach Wireline Transceiver Using a 36-Way Time-Interleaved SAR ADC and Inverter-Based RX Analog Front-End in 7-nm FinFET," IEEE Journal of Solid-State Circuits 56(1), 7-18 (2021).

- Haidang Lin, Charlie Boecker, Masum Hossain, Shankar Tangirala, Roxanne Vu, Socrates D. Vamvakos, Eric Groen, Simon Li, Prashant Choudhary, Nanyan Wang, Masumi Shibata, Hossein Taghavi, Marcus van Ierssel, Adil Hussain Maniyar, Adam Wodkowski, Kulwant Brar, Nhat Nguyen, and Shaishav Desai, "ADC-DSP-Based 10-to-112-Gb/s Multi-Standard Receiver in 7-nm FinFET," IEEE Journal of Solid-State Circuits 56(4), 1265-1277 (2021).

- 40. Yoel Krupnik, Yevgeny Perelman, Itamar Levin, Yosi Sanhedrai, Roee Eitan, Ahmad Khairi, Yizhak Shifman, Yoni Landau, Udi Virobnik, Noam Dolev, Alon Meisler, and Ariel Cohen, "112-Gb/s PAM4 ADC-Based SERDES Receiver With Resonant AFE for Long-Reach Channels," IEEE Journal of Solid-State Circuits 55(4), 1077-1085 (2020).